# A Monolithic AlGaAs/InGaAs Upconverter IC for K-Band Wireless Networks

Mohammad Madihian, *Senior Member, IEEE*, Laurent Desclos, *Member, IEEE*,

Kenichi Maruhashi, *Member, IEEE*, Kazuhiko Onda, *Member, IEEE*, and Masaaki Kuzuhara, *Member, IEEE*

**Abstract**—This paper concerns with the design consideration, fabrication process, and performance of a CPW heterojunction FET (HJFET) upconverter MMIC for K-band wireless system applications. To realize a mixer featuring a simple structure with inherently isolated ports, and yet permitting independent port matching and low LO power operation, a “source injection” concept is introduced by treating the FET as a three-port device in which the IF and LO signals are, respectively, applied to the gate and source terminals, and RF signal is extracted from the drain terminal. The upconverter chip incorporates an HJFET as a mixing element, an IF matching network, an LO matching network, an RF matching network, and an output filter. The upconverter can operate with an LO power level as low as  $-16$  dBm for IF signals in 1.5–2.5 GHz band, and LO signals in 20–23 GHz band. Including a 3 dB pass-band insertion loss of the filter, the upconverter exhibits a maximum conversion gain of  $-6$  dB for an IF power of  $-5$  dBm at 1.9 GHz, and an LO power of  $10$  dBm at 21.5 GHz. LO suppression at IF and RF ports, respectively, is better than  $22$  dB and  $20$  dB, and IF suppression at RF port is better than  $35$  dB.

## I. INTRODUCTION

**R**EBIRTH OF WIRELESS technology and its application to a variety of systems including local area networks, mobile computers, and intelligent highways have urged development of low-cost small-size low-power K-band, V-band, as well as W-band fully monolithic transceiver modules with 1–2 GHz IF frequencies, for facilitating 100–200 Mbps transmission of data, voice, and video [1]–[4]. In a transceiver module, mixers are key-elements for frequency conversion, and require rigorous design methods to achieve an optimum operation. It is desirable to develop mixers featuring a simple structure with inherently isolated ports, and yet permitting independent port matching and low LO power operation.

Conventional FET mixers employ either a “gate mixing” [5], [6] or a “drain injection” [7], [8] topology to produce a desired frequency component, by applying the LO signal to the gate terminal or drain terminal of the device, respectively. In such a structure, since LO signal shares the same port with IF (or RF) signal, independent port matching for each signal is impossible, and to achieve a sufficiently high isolation between LO signal and IF (or RF) signal, usually hybrid circuits such as

Manuscript received February 22, 1995; revised July 10, 1995.

M. Madihian is with Network Research Laboratory, C&C Research Laboratories, NEC Corporation, 4-1-1, Miyazaki, Miyamae-ku, Kawasaki 216 Japan.

L. Desclos was with Network Research Laboratory, C&C Research Laboratories, NEC Corporation, 4-1-1, Miyazaki, Miyamae-ku, Kawasaki 216 Japan. He is now with SILICOM région Ouest, Rennes, France.

K. Maruhashi, K. Onda, and M. Kuzuhara are with Kansai Electronics Research Laboratory, NEC Corporation, 2-9-1 Seiran, Otsu, Shiga 520 Japan.

IEEE Log Number 9415482.

Lange couplers, power dividers as well as balun circuits and several anti-phase input signals are required [9]–[12] which totally increase the mixer circuit complexity. Moreover, since in such a circuit topology the effect of LO signal on the FET transconductance modulation is small, LO signals with high power level are required to perform a satisfactory mixing operation.

Introducing a “source injection” concept, and treating an FET as a “three-port device,” the present paper describes a class of FET mixers for realization of microwave and millimeter-wave frequency converters which exhibit a simple structure and possess the above features.

Circuit design, fabrication process, and experimental results for the case of a K-band upconverter using a  $0.15\mu\text{m} \times 200\mu\text{m}$  AlGaAs/InGaAs heterojunction FET are presented.

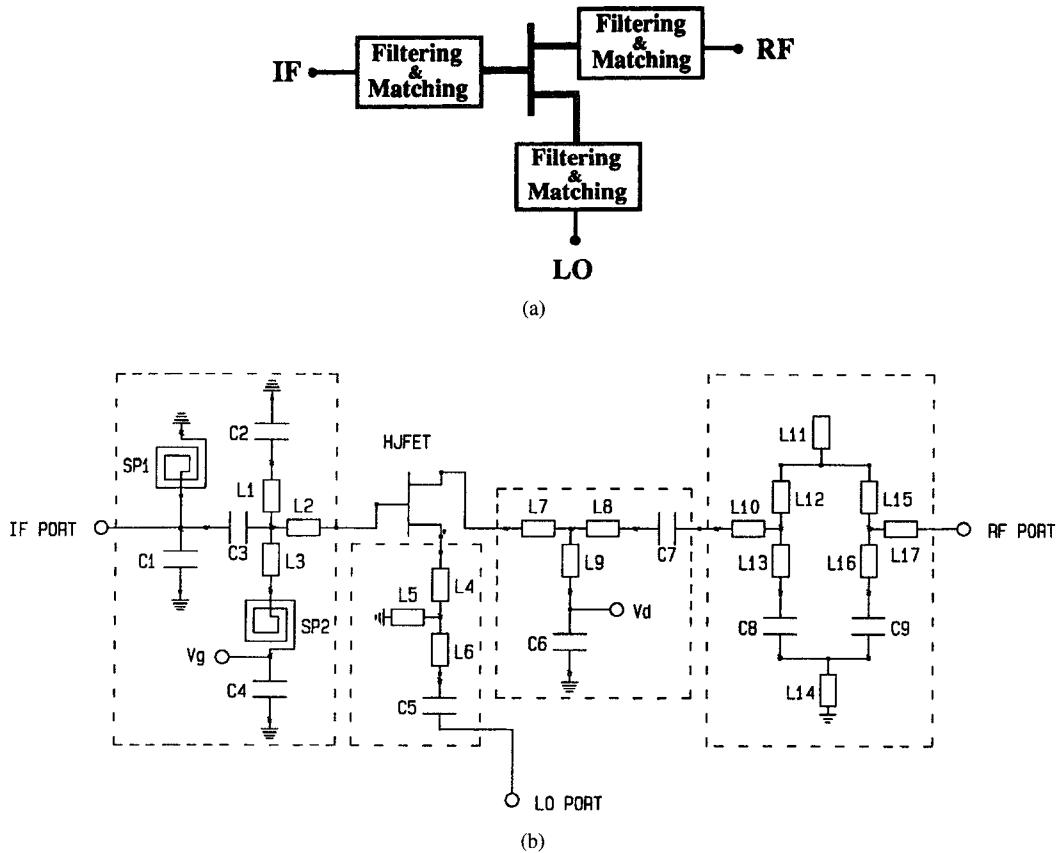

## II. CIRCUIT DESIGN

A block diagram and corresponding equivalent circuit for the CPW K-band upconverter are shown in Fig. 1. The upconverter incorporates an HJFET as a mixing element. IF signal with a frequency of  $f_{\text{IF}}$  is applied to the gate terminal through the IF filtering and matching network, and LO signal with a frequency of  $f_{\text{LO}}$  is applied to the source terminal through the LO filtering and matching network. On the other hand, a resultant upper sideband RF signal having a frequency of  $f_{\text{LO}} + f_{\text{IF}}$  is extracted from the drain terminal, after passing through the RF matching and filtering network and the filter. Use is made of spiral inductors in the IF matching network for resonant type filtering and IF frequency matching. The RF filter consists of two  $T$ -type networks connected in parallel for suppressing the lower sideband frequency ( $f_{\text{LO}} - f_{\text{IF}}$ ) and LO frequency ( $f_{\text{LO}}$ ), but passing upper sideband frequency ( $f_{\text{LO}} + f_{\text{IF}}$ ). The LO matching network is essentially responsible to provide an unconditionally stable operation for the upconverter, both in the presence and absence of an LO signal. The short-circuited transmission line  $L5$  in the LO matching network facilitates transistor’s gate and drain dc biasing.

This structure utilizes the inherent isolation characteristics of the FET terminals under the pinch-off condition to separate the IF, LO, and RF signals without necessity of any hybrid circuit. In the present structure, since the LO signal is directly applied to the source terminal, it has the largest effect on the device transconductance modulation and, consequently, on nonlinear mixing enhancement, which facilitates a low LO power operation.

Fig. 1. K-band upconverter block diagram (a) and corresponding equivalent circuit (b).

Fig. 2. Design steps flow chart.

A flow chart describing major steps in the design of the upconverter, for best operation with a 2.0 GHz IF signal and a 21.5 GHz LO signal, is shown in Fig. 2. Both small signal linear and large signal nonlinear parameters of a discrete  $0.15\mu\text{m} \times 200\mu\text{m}$  AlGaAs/InGaAs HJFET were applied in the circuit design. First, to investigate the stability of the mixer, the three-port network was reduced to a two-port network by replacing the LO source with a  $50\ \Omega$  termination, and stability factor  $K$  and stability measure  $B_1$  were simulated for a

| ELEMENT | VALUE                        | ELEMENT  | VALUE                       |

|---------|------------------------------|----------|-----------------------------|

| L1      | $40\ \Omega, 0.07\ \lambda$  | L12=L15  | $40\ \Omega, 0.02\ \lambda$ |

| L2      | $60\ \Omega, 0.13\ \lambda$  | L13=L16  | $40\ \Omega, 0.14\ \lambda$ |

| L3      | $130\ \Omega, 0.02\ \lambda$ | L14      | $40\ \Omega, 0.30\ \lambda$ |

| L4      | $50\ \Omega, 0.25\ \lambda$  | C1=C2    | $0.4\ \text{pF}$            |

| L5      | $50\ \Omega, 0.02\ \lambda$  | C3=C4    | $10.0\ \text{pF}$           |

| L6      | $50\ \Omega, 0.08\ \lambda$  | C5=C6=C7 | $4.0\ \text{pF}$            |

| L7      | $50\ \Omega, 0.07\ \lambda$  | C8=C9    | $0.1\ \text{pF}$            |

| L8      | $40\ \Omega, 0.10\ \lambda$  | SP1      | $N=7.5$                     |

| L9      | $50\ \Omega, 0.18\ \lambda$  |          | $S=W=10\ \mu\text{m}$       |

| L10=L17 | $50\ \Omega, 0.07\ \lambda$  |          | $L_{in}=300\ \mu\text{m}$   |

| L11     | $50\ \Omega, 0.06\ \lambda$  | SP2      | $SP1 + SP1$                 |

Fig. 3. Optimum value for each element in the matching networks and output filter.

sweeping drain current representing the effect of LO signal on FET transconductance modulation. At this step, unconditional stability of the upconverter was assured by optimizing the series transmission line  $L_4$  in the LO matching network. Then, the  $50\ \Omega$  termination was removed, and a three-port nonlinear harmonic balance circuit analysis was carried out to optimize all matching networks as well as the output filter, for port-matching, conversion gain, and rejection of undesirable frequencies. Finally, the stability of the upconverter was again checked, and if necessary, the series transmission line  $L_4$  was reoptimized, and nonlinear analysis was repeated until all requirements were met. In the analysis, the gate was biased at the pinch-off voltage to realize the maximum mixing effect and minimum power consumption. Fig. 3 summarizes the optimum

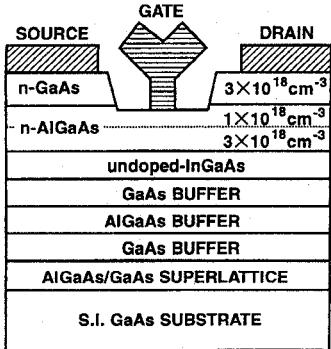

Fig. 4. Cross-sectional view for the step-doped AlGaAs/InGaAs HJFET.

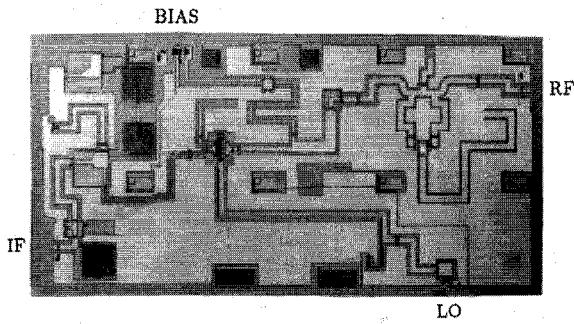

Fig. 5. K-band CPW upconverter MMIC chip. Chip size is 4 mm  $\times$  2 mm.

value for each element in the matching networks and output filter.

### III. FABRICATION PROCESS AND DEVICE CHARACTERISTICS

The K-band upconverter IC was fabricated on a 3-inch undoped SI GaAs substrate. A cross sectional view of an MOCVD step-doped AlGaAs/InGaAs HJFET used in the MMIC is shown in Fig. 4. The epitaxial layer structure consists of an AlGaAs/GaAs superlattice followed by GaAs and AlGaAs buffers, a 13 nm  $In_{0.2}Ga_{0.8}As$  channel, a step-doped 40 nm  $1 \times 10^{18} \text{ cm}^{-3}$ / $3 \times 10^{18} \text{ cm}^{-3}$   $Al_{0.2}Ga_{0.8}As$ , and an 80 nm  $3 \times 10^{18} \text{ cm}^{-3}$   $n^+$ -GaAs cap layer. In the FET fabrication process, mesa-isolation, conventional photolithography, electron beam evaporation and lift-off techniques have been employed. A CPW structure was used for transmission lines which permits chip size reduction and possibility of realizing transmission lines with different characteristics impedances without affecting the overall chip layout. To suppress odd modes, metal bridges were employed extensively to connect ground planes along the line particularly in the vicinity of a line discontinuity. An MIM structure was applied for fabricating resonant capacitors in IF matching network, dc blocking capacitors and bypass capacitors. Details of the fabrication process have been reported elsewhere [13], [14]. The HJFET used in the upconverter IC has a gate length of 0.15  $\mu\text{m}$  and a total gate width of 200  $\mu\text{m}$  (25  $\mu\text{m}$   $\times$  8 fingers). The device has a typical transconductance of 380 mS/mm and an  $f_T$  of 70 GHz both at a drain bias of 2 V with a reverse gate-drain breakdown voltage of 11 V, and a pinch-off voltage

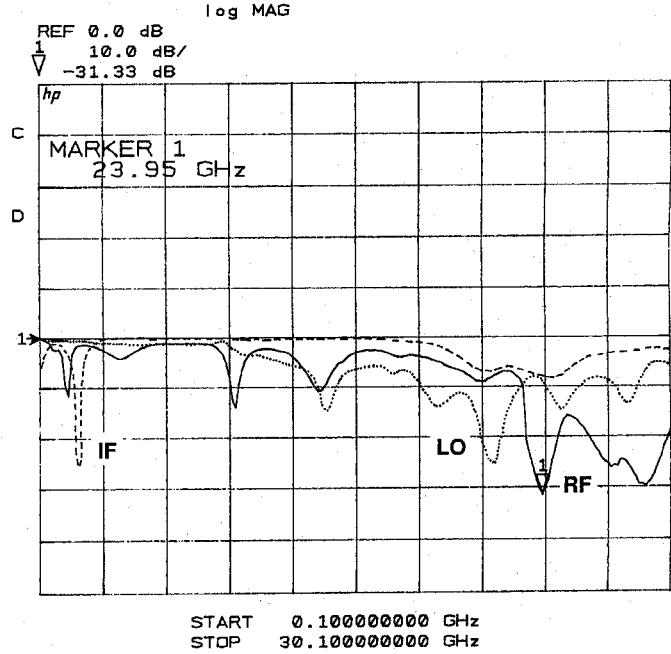

Fig. 6. Small signal matching characteristics for IF, LO, and RF ports.

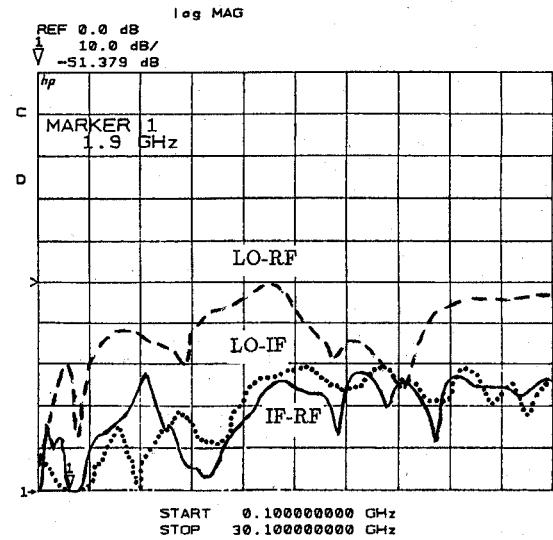

Fig. 7. Small signal LO-IF, LO-RF, and IF-RF port isolation.

of  $-1.4$  V. Measured minimum noise figure for the device is 1.1 dB at 24 GHz with an associated gain of 9.5 dB.

### IV. PERFORMANCE

Fig. 5 shows the chip photograph for the complete K-band CPW upconverter IC. Chip size is 4 mm  $\times$  2 mm. On-wafer Cascade Microtech probes were utilized to evaluate the chip performance. The FET gate bias was  $-1.4$  V, corresponding to the pinch-off voltage, and the drain bias was 0.8 V. Fig. 6 shows small signal matching characteristics for the IF, LO, and RF ports. Measured in-band return loss for each port is better than 25 dB. Fig. 7 represents small signal LO to IF, LO to RF, and IF to RF port isolation for the upconverter. LO suppression at IF and RF ports is, respectively, better than 22

(a)

(b)

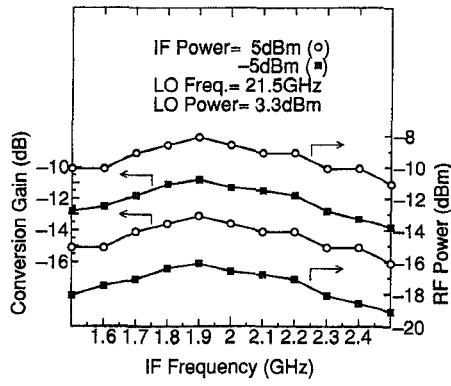

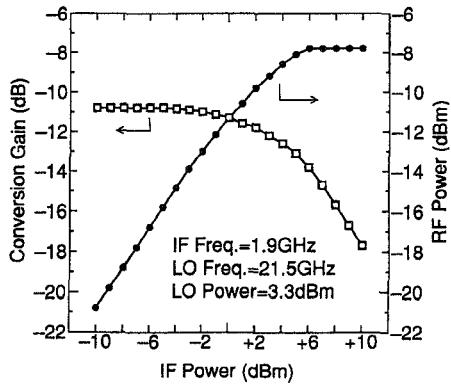

Fig. 8. Conversion gain and RF output power versus IF frequency (a) and power (b).

dB and 20 dB, and IF suppression at RF port is better than 35 dB. On the other hand, measured pass-band and rejection-band insertion loss for the output filter were, respectively, 3 dB and 18 dB, at an IF frequency of 2 GHz, and an LO frequency of 22 GHz. The filter, however, exhibited a graceful behavior change for an IF frequency in 1.5 to 2.5 GHz.

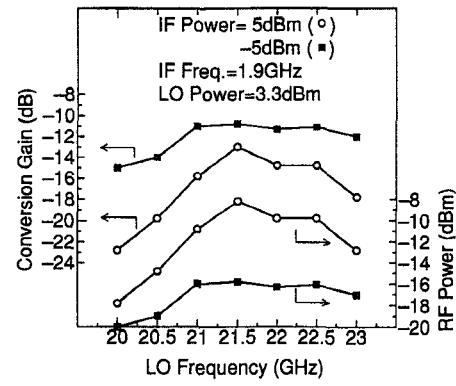

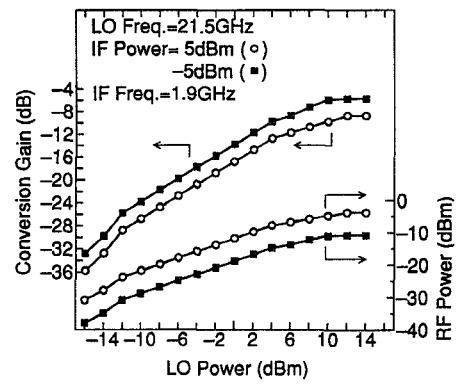

Large signal upconverter measurement results for the upper sideband frequency component are shown in Figs. 8 and 9. Fig. 8(a) depicts conversion gain as well as RF output power variation versus IF frequency for an LO power of 3.3 dBm, an LO frequency of 21.5 GHz, and IF power levels of -5 dBm and +5 dBm. Fig. 8(b) represents conversion gain and RF output power against IF power for an LO power of 3.3 dBm, an LO frequency of 21.5 GHz and an IF frequency of 1.9 GHz. Conversion gain is constant for IF power levels lower than 2 dBm, and reduces with increasing IF power, for which RF output power saturates. Fig. 9(a) exhibits conversion gain as well as RF output power variation versus LO frequency for an LO power of 3.3 dBm, an IF frequency of 1.9 GHz, and IF power levels of -5 dBm and +5 dBm. Fig. 9(b) represents conversion gain and RF output power against LO power for an LO frequency of 21.5 GHz, an IF frequency of 1.9 GHz, and IF power levels of -5 dBm and +5 dBm. The upconverter operates with LO power levels as low as -10 dBm, and maximum conversion gain is -6 dB which is obtained for an IF power of -5 dBm and an LO power of 10 dBm. On

(a)

(b)

Fig. 9. Conversion gain and RF output power versus LO frequency (a) and power (b).

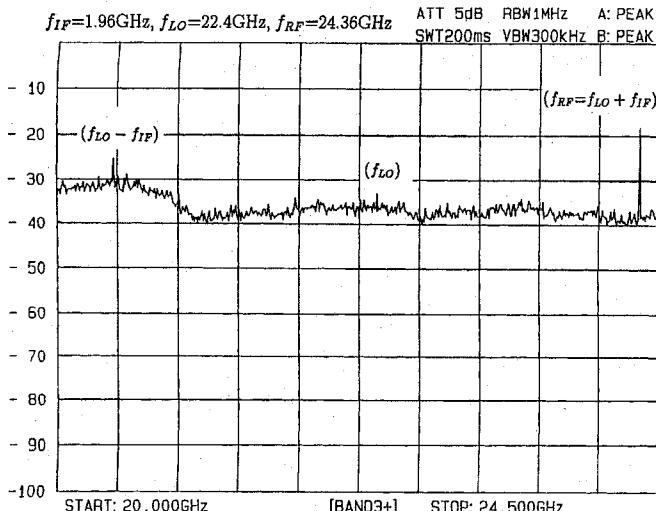

the other hand, maximum output power is -3 dBm which is obtained for an IF power of 5 dBm and an LO power higher than 10 dBm. Both conversion gain and RF output power saturates for an LO power level higher than 10 dBm. A typical output spectra for the upconverter is depicted in Fig. 10. From the figure, suppression of the LO and LSB signals at the output port is, respectively, better than 18 dB and 16 dB. However, due to bandwidth limitation of the measurement system, the LSB signal spectrum is not displayed correctly.

No spurious oscillation was observed, and the upconverter was stable for an input IF signal in -10 to +10 dBm range, an input LO signal in -20 to +20 dBm range, and any gate voltage between 0 and -2 V. Experiments reported in this paper have been carried out at an ambient temperature. The upconverter performance is, however, anticipated not to be drastically affected by a change in the temperature, since the device is biased at the pinch-off voltage and the input LO power level is not remarkably high.

## V. CONCLUSION

Design consideration and performance of a CPW upconverter MMIC for K-band wireless system applications were described. In the circuit design, the FET was treated as a three-port device in which the LO signal is applied to the source terminal. Including a 3 dB pass-band insertion loss of the filter, the upconverter exhibits a maximum conversion gain

Fig. 10. A typical output spectra for the developed upconverter.

of  $-6$  dB, and a maximum output power of  $-3$  dBm. In the present paper, we described the "source injection" concept for the case of a K-band upconverter. The same design approach could be applied to realization of microwave/millimeter-wave downconverters, as well.

#### ACKNOWLEDGMENT

Thanks are due to N. Goto for large signal measurement arrangement, N. Hayama and H. Takahashi for helping hands, and Y. Ohno for encouragement. Support from S. Hasegawa and H. Abe is appreciated.

#### REFERENCES

- [1] D. Skellern and T. Percival, "High speed wireless LANs: Technologies for missing link," in *1994 IEEE MMWMC-S Dig.*, May 1994.

- [2] Y. Takimoto and T. Ihara, "Research activities on millimeter wave indoor communication systems in Japan," in *1993 IEEE MTT-S Dig.*, June 1993, p. 673.

- [3] J. Loraine, "Wireless data networks: An opportunity for GaAs," in *1993 IEEE GaAs IC Symp. Dig.*, Oct. 1993, p. 11.

- [4] H. R. Malone, M. Dydyk, D. Mathews, V. Nair, G. B. Norris, and W. Seely, "High volume GaAs MMIC applications," in *1991 IEEE GaAs IC Symp. Dig.*, Oct. 1991, p. 135.

- [5] R. A. Pucel, D. Massé and R. Bera, "Performance of GaAs MESFET mixers at X-band," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-24, p. 351, June 1976.

- [6] C. C. Penáloza and C. Aichison, "Analysis and design of MESFET gate mixer," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-35, p. 643, July 1987.

- [7] P. Bura and R. Dikshit, "FET mixer with the drain LO injection," *Electron. Lett.*, vol. 12, no. 20, p. 536, Sept. 1976.

- [8] G. Tomassetti, "An unusual microwave mixer," in *Proc. Eur. Microwave Conf.*, 1986, p. 754.

- [9] V. Brady, T. Hsu, R. Reeves, and M. Vermeulen, "Development of a monolithic FET Ka-band single side band upconverter and image reject downconverter," in *1989 IEEE GaAs IC Symp. Dig.*, Oct. 1989, p. 189.

- [10] W. R. Brinlee, A. M. Pavio, C. L. Goldsmith, and W. J. Thompson, "A monolithic multifunction EW broadband receiver converter," in *1993 IEEE GaAs IC Symp. Dig.*, Oct. 1993, p. 207.

- [11] T. Hirota and M. Muraguchi, "K-band frequency up-converters using reduced-size couplers and dividers," in *1991 IEEE GaAs IC Symp. Dig.*, Oct. 1991, p. 53.

- [12] A. Minakawa and T. Hirota, "An extremely small 26 GHz monolithic image-rejection mixer without DC power consumption," *IEEE Trans. Microwave Theory Tech.*, vol. 41, p. 1634, Sept. 1993.

- [13] N. Samoto, Y. Makino, K. Onda, E. Mizuki, and T. Itoh, "A novel electron-beam exposure technique for  $0.1 \mu\text{m}$  T-shaped gate fabrication," *J. Vac. Sci. Technol.*, vol. B8, no. 6, p. 1335, Nov./Dec. 1990.

- [14] Y. Nashimoto, S. Ichikawa, N. Samoto, K. Onda, M. Kuzuhara, and K. Arai, "Super-low noise heterojunction field-effect transistors (HJFET's) with  $0.2 \mu\text{m}$  T-shaped 8 gate fingers," *NEC Research & Development* vol. 33, no. 3, p. 268, July 1992.

**Mohammad Madihian** (S'81-M'83-SM'88) was born in Tehran, Iran, on January 3, 1954. He received the B.Sc. degree from Iran University of Science and Technology, Tehran, Iran, in 1976, and the M.Sc. and Ph.D. degrees from Shizuoka University, Hamamatsu, Japan, in 1980 and 1983, respectively, all in electronic engineering.

In 1983, he joined NEC Microelectronics Research Laboratories, Kawasaki, Japan, where he has worked on research and development of compound semiconductor device-based digital as well as microwave monolithic IC's. From 1989 to 1991, he was the Chief Technical Advisor to NEC Tehran Office and Iran Telecommunications Industries Company. He is presently a Principal Researcher at NEC C&C Research Laboratories, where he conducts research and development of GaAs-based monolithic millimeter-wave IC's and BiCMOS-based MMIC's for high speed wireless LAN and personal communications applications.

Dr. Madihian has received the 1988 IEEE Microwave Prize. Since 1994, he has been serving on the IEEE GaAs IC Symposium Technical Program Committee.

**Laurent Desclos** (M'95) was born in Sélestat, France on January 30, 1966. He received the B.Sc. and Ph.D. degree from National Institute of Applied Sciences, Rennes, France, respectively, in 1988 and 1992, in electrical engineering.

From 1988 to 1989 he was in Gabon to work on Earth Station Communications systems. From 1992 to 1994, he was with NEC C&C Research Laboratories, Kawasaki, Japan, to work on the design of GaAs MMIC's for wireless communications application. Since 1994, he has been with Silicon Région Ouest, Rennes, France, as an Electromagnetic Compatibility Domain Consultant.

Dr. Desclos has published in different areas such as active antenna, radar cross section calculation and measurement, and near field problems including coupling effects, using Physical Optics Methods.

**Kenichi Maruhashi** (M'95) was born in Aichi, Japan, on February 11, 1967. He received the B.S. and M.S. degree in physics from Kobe University, Kobe, Japan, in 1989 and 1991, respectively. In 1991, he joined NEC Corporation, Shiga, Japan, where he works on modeling, design and characterization of heterojunction FET's, and development MMIC's based on their technology. His current research interest includes microwave and millimeter-wave integrated circuits for high-speed wireless communication systems.

Mr. Maruhashi is a member of the Institute of Electronics, Information and Communication Engineers of Japan.

**Kazuhiko Onda** (M'91) was born in Tokyo, Japan, on Oct. 25, 1960. He received the B.S. degree in physics from Tokyo Institute of Technology, Tokyo, Japan, in 1984, and received the M.S. degrees in physics from University of Tokyo, Tokyo, Japan, in 1986, respectively. In 1986, he joined NEC Corporation, Kawasaki, Japan, where he worked on compound semiconductor devices for microwave and millimeter-wave low noise applications. From 1994 to 1995, he spent an academic year at the University of Illinois at Urbana-Champaign, where he worked on modeling and simulation of high-speed III-V heterojunction devices. His current research interest includes GaAs-based and InP-based heterojunction FET, HBT and MMIC technology. He is now an Assistant Manager of the Kansai Electronics Research Laboratory, Shiga, Japan, NEC Corporation.

Mr. Onda is a member of the Japan Society of Applied Physics and the Institute of Electronics, Information and Communication Engineers of Japan.

**Masaaki Kuzuhara** (M'82) was born in Osaka, Japan, on November 5, 1955. He received the B.S., M.S., and Ph.D. degrees in electrical engineering from Kyoto University, Kyoto, Japan, in 1979, 1981 and 1991, respectively.

In 1981, he joined NEC Corporation, Kawasaki, Japan, where he worked on the application of rapid thermal processing to GaAs integrated circuits. From 1987 to 1988, he spent an academic year at the University of Illinois at Urbana-Champaign, where he worked on modeling of high-speed III-V heterojunction devices. His current research interest includes modeling, design, and testing of heterojunction field-effect transistors for use in microwave circuits. He is now a Research Manager of the Kansai Electronics Research Laboratory, Shiga, Japan, NEC Corporation.

Dr. Kuzuhara is a member of the Japan Society of Applied Physics and the Institute of Electronics, Information and Communication Engineers of Japan.